Documente tehnice

Specificatii

Marca

NexperiaLogic Family

HC

Logic Function

D Type

Input Type

Single Ended

Tip iesire

3 State

Output Signal Type

Single Ended

Triggering Type

Positive Edge

Polarity

Non-Inverting

Timp montare

Surface Mount

Tip pachet

SOIC

Numar pini

16

Set/Reset

Master Reset

Number of Elements per Chip

4

Maximum Propagation Delay Time @ Maximum CL

175 ns @ 2 V

Maximum Operating Supply Voltage

6 V

Dimensiuni

10 x 4 x 1.45mm

Temperatura maxima de lucru

+125 °C

Propagation Delay Test Condition

50pF

Lungime

10mm

Inaltime

1.45mm

Latime

4mm

Temperatura minima de lucru

-40 °C

Minimum Operating Supply Voltage

2 V

Tara de origine

Thailand

Detalii produs

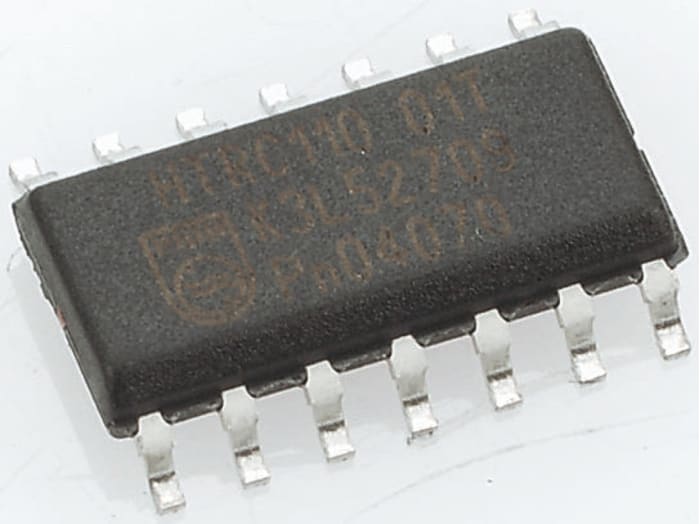

74HC Family Flip-Flops & Latches, Nexperia

A range of NXP Flip-Flops and Latches from the 74HC Family of CMOS Logic ICs. The 74HC Family use silicon gate CMOS technology to achieve operating speeds similar to the LSTTL family but with the low power consumption of standard CMOS integrated circuits.

74HC Family

€ 23,00

€ 0,46 Each (In a Tube of 50) (fara TVA)

€ 27,37

€ 0,547 Each (In a Tube of 50) (cu TVA)

50

€ 23,00

€ 0,46 Each (In a Tube of 50) (fara TVA)

€ 27,37

€ 0,547 Each (In a Tube of 50) (cu TVA)

50

Informatii despre stoc temporar indisponibile

Incercati din nou mai tarziu

Documente tehnice

Specificatii

Marca

NexperiaLogic Family

HC

Logic Function

D Type

Input Type

Single Ended

Tip iesire

3 State

Output Signal Type

Single Ended

Triggering Type

Positive Edge

Polarity

Non-Inverting

Timp montare

Surface Mount

Tip pachet

SOIC

Numar pini

16

Set/Reset

Master Reset

Number of Elements per Chip

4

Maximum Propagation Delay Time @ Maximum CL

175 ns @ 2 V

Maximum Operating Supply Voltage

6 V

Dimensiuni

10 x 4 x 1.45mm

Temperatura maxima de lucru

+125 °C

Propagation Delay Test Condition

50pF

Lungime

10mm

Inaltime

1.45mm

Latime

4mm

Temperatura minima de lucru

-40 °C

Minimum Operating Supply Voltage

2 V

Tara de origine

Thailand

Detalii produs

74HC Family Flip-Flops & Latches, Nexperia

A range of NXP Flip-Flops and Latches from the 74HC Family of CMOS Logic ICs. The 74HC Family use silicon gate CMOS technology to achieve operating speeds similar to the LSTTL family but with the low power consumption of standard CMOS integrated circuits.